### 1 概述

SW3203 是一个高效率的同步 4 管升降压控制器,输入电压支持 3 到 28V,输出电压支持 3 到 22V,可以满足客户的不同需求。输出电压支持 I2C 控制和 FB 控制,可以提供最大 100W 的功率输出,支持多路输入输出检测及通路驱动,在支持不同应用需求的同时还简化了方案设计。

## 2 应用领域

- 车载充电器

- 电子烟

- 电源适配器

- USB Hub

- 智能 USB 插座

- 工业设备

## 3 规格

### · 升降压 DCDC

- ➤ 支持 100W 输出功率

- ▶ 支持 3V-28V 输入电压

- ▶ 支持 3V-22V 输出电压

- ▶ 可灵活选择 FB/I2C 调压方式

- ➤ 开关频率 200KHz/300KHz/400KHz /800KHz 可选

- ▶ 支持 I2C 编程控制输出限流

- ▶ PFM/PWM 模式随负载大小自动 切换

- > 升压和降压之间无缝切换

#### • 端口接入检测

▶ 2个负载接入检测

- 12bit 高精度 ADC

- · 通路 MOS 驱动

- ▶ 集成 3 个 NMOS 驱动,简化电路设计

### • 完善的保护机制

- ▶ 输入过压保护

- ▶ 输出过压保护

- ▶ 输出过流保护

- ▶ 输出短路保护

- ▶ 电感峰值限流保护

- ▶ 芯片过温保护

- I2C 接口

- QFN-32(4x4mm) 封装

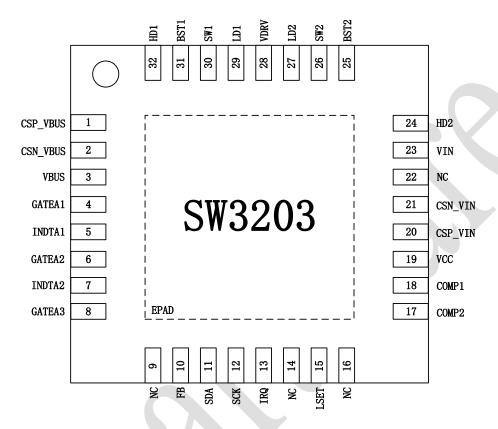

## 4 引脚定义及功能描述

## 4.1 引脚定义

### 4.2 引脚描述

| Pin | Name     | Function Description               |

|-----|----------|------------------------------------|

|     |          | VBUS 端电流采样正极。为了避免受到检流信号受到高         |

|     |          | 频噪声影响和检流的稳定,需要在 VBUS 检流电阻上并        |

| 1   | CSP_VBUS | 一个 100nF 的电容,还需要在检流电阻与 CSP_VBUS 之  |

|     |          | 间加入一个低通滤波器,低通滤波器的设计请参考             |

|     |          | "9.2.3 VBUS 端检流低通滤波器参数选择"。         |

|     |          | Vbus 端电流采样负极。为了避免受到检流信号受到高频        |

|     |          | 噪声影响和检流的稳定,需要在 VBUS 检流电阻上并一        |

| 2   | CSN_VBUS | 个 100nF 的电容,还需要在检流电阻与 CSN_VBUS 之   |

|     |          | 间加入一个低通滤波器,低通滤波器的设计请参考             |

|     |          | "9.2.3 VBUS 端检流低通滤波器参数选择"。         |

| 3   | VBUS     | 芯片供电, VBUS 电压检测。                   |

|     |          | Nmos 通路管驱动 1。此驱动使用 chargepump 实现,驱 |

| 4   | GATEA1   | 动能力较弱,使用通路管驱动时,通路 NMOS 推荐选择        |

| 4   | GAIEAI   | 栅源漏电流不大于 100nA 的 NMOS。不使用通路管驱      |

|     |          | 动,GATEA1 保持 floating 即可。           |

|    |         | 文11 120 江南州州 <b>(1</b> 45) 11十2                                                                                    |

|----|---------|--------------------------------------------------------------------------------------------------------------------|

| 5  | INDTA1  | 负载接入检测 1。使用此功能检测负载接入时,INDTA1上必须设置一个不小于 4.7uF 的接地电容,此电容推荐值为 10uF。                                                   |

| 6  | GATEA2  | Nmos 通路管驱动 2。此驱动使用 chargepump 实现,驱动能力较弱,使用通路管驱动时,通路 NMOS 推荐选择栅源漏电流不大于 100nA 的 NMOS。不使用通路管驱动,GATEA2 保持 floating 即可。 |

| 7  | INDTA2  | 负载接入检测 2。使用此功能检测负载接入时,INDTA2<br>上必须设置一个不小于 4.7uF 的接地电容,此电容推荐<br>值为 10uF。                                           |

| 8  | GATEA3  | Nmos 通路管驱动 3。此驱动使用 chargepump 实现,驱动能力较弱,使用通路管驱动时,通路 NMOS 推荐选择栅源漏电流不大于 100nA 的 NMOS。不使用通路管驱动,GATEA3 保持 floating 即可。 |

| 9  | NC      | 未使用,请保持 floating。                                                                                                  |

| 10 | FB      | VBUS 输出电压外部反馈。FB 的电压固定为 0.5V。未使用外部反馈设置输出电压时,FB 处于 floating 状态。                                                     |

| 11 | SDA     | I2C Data。请将 SDA 连接到 host controller,推荐 SDA<br>上拉电阻选择 10KΩ。                                                         |

| 12 | SCK     | I2C Clock。请将 SCL 连接到 host controller,推荐 SCL<br>上拉电阻选择 10KΩ。                                                        |

| 13 | IRQ     | I2C Interrupt。IRQ 为开漏输出,推荐使用 10KΩ 电阻触 发事件中断时 IRQ 输出低电平直到事件中断标志位被清 除。                                               |

| 14 | NC      | 未使用,请保持 floating。                                                                                                  |

| 15 | LSET    | 电感值设置,可设置 4 种不同的电感值。10KΩ 设置为 1uH, 20 KΩ 设置为 2.2uH, 30KΩ 设置为 3.3uH, 43KΩ 设置为 4.7uH。此设置必须与外部电感值一致,否则会导致工作异常。         |

| 16 | NC      | 未使用,请保持 floating。                                                                                                  |

| 17 | COMP2   | CC 环路补偿。COMP2 具体的 RC 补偿网络请参考 "9.2.2 COMP 补偿 RC 参数选择"                                                               |

| 18 | COMP1   | CV 环路补偿。COMP1 具体的 RC 补偿网络请参考 "9.2.2 COMP 补偿 RC 参数选择"                                                               |

| 19 | VCC     | 由 VBUS 或者 VIN 提供的 5V 线性调节器输出。5V 线性调节器在 buckboost 工作时启动。VCC 需要在靠近芯片 VCC 引脚处设置一个 10uF 的对地电容。                         |

| 20 | CSP_VIN | VIN 端电流采样正极。为了保证检流的稳定,需要在<br>VIN 检流电阻上并一个 100nF 的电容。如果不需要 VIN<br>端检流,请将 CSP_VIN 与 VIN 短接。                          |

| 21 | CSN_VIN | VIN 端电流采样负极。为了保证检流的稳定,需要在<br>VIN 检流电阻上并一个 100nF 的电容。如果不需要 VIN<br>端检流,请将 CSN_VIN 与 VIN 短接。                          |

| 22   NC   未使用,请保持 floating。   23   VIN   芯片供电,VIN 电压采样。   24   HD2   VIN 端上管 gate 驱动。需要连接到 VIN 端半桥高侧 NMOS (Q4) 的 gate   VIN 端上管 bootstrap。需要在 HD2-BST2 之间接入一个 100nF 的电容。VDRV 和 BST2 的自举二极管集成在芯片内部。   VIN 端 switching 点。SW2 需要连接到 VIN 端半桥高侧 NMOS (Q4) 的源极。   VIN 端下管 gate 驱动。需要连接到 VIN 端半桥低侧 NMOS (Q3) 的 gate   由 VBUS 或者 VIN 提供的 5.5V 线性调节器输出。5.5V 线性调节器在非体眠状态时启动。VDRV 需要在靠近芯片 VDRV 引脚处设置一个 10uF 的对地电容。   VBUS 端下管 gate 驱动。需要连接到 VBUS 端半桥低侧 NMOS (Q2) 的 gate   VBUS 端 switching 点。SW1 需要连接到 VBUS 端半桥高侧 NMOS (Q1) 的源极。   VBUS 端 switching 点。SW1 需要连接到 VBUS 端半桥高侧 NMOS (Q1) 的源极。   VBUS 端上管 bootstrap。需要在 HD1-BST1 之间接入一个 100nF 的电容。VDRV 和 BST1 的自举二极管集成在 芯片内部。   VBUS 端上管 gate 驱动。需要连接到 VBUS 端半桥高侧 NMOS (Q1) 的 gate   VBUS 端上管 gate 驱动。需要连接到 VBUS 端半桥高侧 NMOS (Q1) 的 gate   VBUS 端上管 gate 驱动。需要连接到 VBUS 端半桥高侧 NMOS (Q1) 的 gate   VBUS 端上管 gate 驱动。需要连接到 VBUS 端半桥高侧 NMOS (Q1) 的 gate   VBUS 端上管 gate 驱动。需要连接到 VBUS 端半桥高侧 NMOS (Q1) 的 gate   VBUS 端上管 gate 驱动。需要连接到 VBUS 端半桥高侧 NMOS (Q1) 的 gate   VBUS 端上管 gate 驱动。需要连接到 VBUS 端半桥高侧 NMOS (Q1) 的 gate   VBUS MATE (Q1 EBAD EBAD EBAD EBAD EBAD EBAD EBAD EBAD |    |         | 文的 120 江南的向从平向少万阵                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|---------|---------------------------------------|

| VIN 端上管 gate 驱动。需要连接到 VIN 端半桥高侧 NMOS(Q4)的 gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 22 | NC      | 未使用,请保持 floating。                     |

| NMOS (Q4) 的 gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 23 | VIN     | 芯片供电, VIN 电压采样。                       |

| NMOS(Q4)的 gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 24 | IID3    | VIN 端上管 gate 驱动。需要连接到 VIN 端半桥高侧       |

| 25   BST2   100nF 的电容。VDRV 和 BST2 的自举二极管集成在芯片内部。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 24 | HD2     | NMOS (Q4) 的 gate                      |

| 26       SW2       VIN 端 switching 点。SW2 需要连接到 VIN 端半桥高侧 NMOS(Q4)的源极。         27       LD2       VIN 端下管 gate 驱动。需要连接到 VIN 端半桥低侧 NMOS(Q3)的 gate         28       VDRV       想性调节器在非休眠状态时启动。VDRV 需要在靠近芯片 VDRV 引脚处设置一个 10uF 的对地电容。         29       LD1       VBUS 端下管 gate 驱动。需要连接到 VBUS 端半桥低侧 NMOS(Q2)的 gate         30       SW1       VBUS 端 switching 点。SW1 需要连接到 VBUS 端半桥高侧 NMOS(Q1)的源极。         31       BST1       个 100nF 的电容。VDRV 和 BST1 的自举二极管集成在芯片内部。         32       HD1       VBUS 端上管 gate 驱动。需要连接到 VBUS 端半桥高侧 NMOS(Q1)的 gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |         | VIN 端上管 bootstrap。需要在 HD2-BST2 之间接入一个 |

| VIN 端 switching 点。SW2 需要连接到 VIN 端半桥高侧 NMOS(Q4)的源极。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 25 | BST2    | 100nF的电容。VDRV和BST2的自举二极管集成在芯          |

| NMOS(Q4)的源极。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |         | 片内部。                                  |

| NMOS(Q4)的源极。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 26 | CWO     | VIN 端 switching 点。SW2 需要连接到 VIN 端半桥高侧 |

| NMOS (Q3) 的 gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 26 | SW2     | NMOS (Q4) 的源极。                        |

| NMOS(Q3)的 gate   由 VBUS 或者 VIN 提供的 5.5V 线性调节器输出。5.5V 线性调节器在非体眠状态时启动。VDRV 需要在靠近芯片 VDRV 引脚处设置一个 10uF 的对地电容。 VBUS 端下管 gate 驱动。需要连接到 VBUS 端半桥低侧 NMOS(Q2)的 gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 27 | 1.00    | VIN 端下管 gate 驱动。需要连接到 VIN 端半桥低侧       |

| 28VDRV线性调节器在非休眠状态时启动。VDRV 需要在靠近芯片 VDRV 引脚处设置一个 10uF 的对地电容。29LD1VBUS 端下管 gate 驱动。需要连接到 VBUS 端半桥低侧 NMOS (Q2) 的 gate30SW1VBUS 端 switching 点。SW1 需要连接到 VBUS 端半桥高侧 NMOS (Q1) 的源极。31BST1VBUS 端上管 bootstrap。需要在 HD1-BST1 之间接入一个 100nF 的电容。VDRV 和 BST1 的自举二极管集成在芯片内部。32HD1VBUS 端上管 gate 驱动。需要连接到 VBUS 端半桥高侧 NMOS (Q1) 的 gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 27 | LD2     | NMOS (Q3) 的 gate                      |

| 片 VDRV 引脚处设置一个 10uF 的对地电容。29LD1VBUS 端下管 gate 驱动。需要连接到 VBUS 端半桥低侧 NMOS (Q2) 的 gate30SW1VBUS 端 switching 点。SW1 需要连接到 VBUS 端半桥高侧 NMOS (Q1) 的源极。31BST1VBUS 端上管 bootstrap。需要在 HD1-BST1 之间接入一个 100nF 的电容。VDRV 和 BST1 的自举二极管集成在芯片内部。32HD1VBUS 端上管 gate 驱动。需要连接到 VBUS 端半桥高侧 NMOS (Q1) 的 gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |         | 由 VBUS 或者 VIN 提供的 5.5V 线性调节器输出。5.5V   |

| 29LD1VBUS 端下管 gate 驱动。需要连接到 VBUS 端半桥低侧 NMOS (Q2) 的 gate30SW1VBUS 端 switching 点。SW1 需要连接到 VBUS 端半桥高侧 NMOS (Q1) 的源极。31BST1VBUS 端上管 bootstrap。需要在 HD1-BST1 之间接入一个 100nF 的电容。VDRV 和 BST1 的自举二极管集成在芯片内部。32HD1VBUS 端上管 gate 驱动。需要连接到 VBUS 端半桥高侧 NMOS (Q1) 的 gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 28 | 28 VDRV | 线性调节器在非休眠状态时启动。VDRV 需要在靠近芯            |

| NMOS(Q2)的 gate  VBUS 端 switching 点。SW1 需要连接到 VBUS 端半桥高侧 NMOS(Q1)的源极。  VBUS 端上管 bootstrap。需要在 HD1-BST1 之间接入一个 100nF 的电容。VDRV 和 BST1 的自举二极管集成在芯片内部。  VBUS 端上管 gate 驱动。需要连接到 VBUS 端半桥高侧 NMOS(Q1)的 gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |         | 片 VDRV 引脚处设置一个 10uF 的对地电容。            |

| NMOS(Q2)的 gate  VBUS 端 switching 点。SW1 需要连接到 VBUS 端半桥高侧 NMOS(Q1)的源极。  VBUS 端上管 bootstrap。需要在 HD1-BST1 之间接入一个 100nF 的电容。VDRV 和 BST1 的自举二极管集成在芯片内部。  VBUS 端上管 gate 驱动。需要连接到 VBUS 端半桥高侧 NMOS(Q1)的 gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 20 | I D1    | VBUS 端下管 gate 驱动。需要连接到 VBUS 端半桥低侧     |

| 30SW1高侧 NMOS(Q1)的源极。31BST1VBUS 端上管 bootstrap。需要在 HD1-BST1 之间接入一个 100nF 的电容。VDRV 和 BST1 的自举二极管集成在芯片内部。32HD1VBUS 端上管 gate 驱动。需要连接到 VBUS 端半桥高侧 NMOS(Q1)的 gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 29 | LDI     | NMOS (Q2) 的 gate                      |

| 高侧 NMOS(Q1)的源极。  VBUS 端上管 bootstrap。需要在 HD1-BST1 之间接入一个 100nF 的电容。VDRV 和 BST1 的自举二极管集成在芯片内部。  VBUS 端上管 gate 驱动。需要连接到 VBUS 端半桥高侧 NMOS(Q1)的 gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 20 | CW/1    | VBUS 端 switching 点。SW1 需要连接到 VBUS 端半桥 |

| 31BST1个 100nF 的电容。VDRV 和 BST1 的自举二极管集成在 芯片内部。32HD1VBUS 端上管 gate 驱动。需要连接到 VBUS 端半桥高侧 NMOS(Q1)的 gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 30 | SW1     | 高侧 NMOS(Q1)的源极。                       |

| 芯片内部。  VBUS 端上管 gate 驱动。需要连接到 VBUS 端半桥高侧 NMOS(Q1)的 gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |         | VBUS 端上管 bootstrap。需要在 HD1-BST1 之间接入一 |

| VBUS 端上管 gate 驱动。需要连接到 VBUS 端半桥高侧 NMOS(Q1)的 gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 31 | BST1    | 个 100nF 的电容。VDRV 和 BST1 的自举二极管集成在     |

| NMOS (Q1) 的 gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |         | 芯片内部。                                 |

| NMOS (Q1) 的 gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 22 | LID1    | VBUS 端上管 gate 驱动。需要连接到 VBUS 端半桥高侧     |

| 艾比斯的相称 金甲拉列中海拉斯亚里 伊江 EDAD F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 32 | ни      | NMOS (Q1) 的 gate                      |

| 心月地的片盆,而安按到电源按地干面,保证 EPAD 与                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |         | 芯片地的焊盘,需要接到电源接地平面,保证 EPAD 与           |

| / <b>EPAD</b> 电路板保持良好的连接关系,可以保证工作性能和良好                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | /  | EPAD    | 电路板保持良好的连接关系,可以保证工作性能和良好              |

| 的散热。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |         | 的散热。                                  |

## 5 极限参数

| Parameters | Symbol                    | MIN  | MAX  | UNIT |

|------------|---------------------------|------|------|------|

| VBUS 端电压   | VBUS/FB/CSN_VBUS/         | -0.3 | 35   | V    |

| VDUS 编电压   | CSP_VBUS                  | -0.3 | 33   | V    |

| VIN 端电压    | CSN_VIN/CSP_VIN/          | -0.3 | 35   | V    |

| VIIV师电压    | VIN                       | -0.3 | 33   | V    |

| 开关驱动       | HD1/HD2/BST1/BST2         | -0.3 | 40   | V    |

| SW 电压      | SW1/SW2                   | -0.3 | 35   | V    |

| 端口电压       | 端口电压 INDTA1/INDTA2/INDTA3 |      | 35   | V    |

| 通路控制       | 通路控制 GATEA1/GATEA2        |      | 40   | V    |

| 其它管脚电压     | 其它管脚电压                    |      | 7    | V    |

| 节温         |                           | -40  | +150 | °C   |

| 存储温度       | 存储温度                      |      | +150 | °C   |

| ESD (HBM)  |                           | -4   | +4   | KV   |

【备注】超过此范围的电压电流及温度等条件可能导致器件永久损坏。

## 6 推荐参数

| Parameters | Symbol | MIN | Typical | MAX | UNIT |

|------------|--------|-----|---------|-----|------|

| 输入电压       | VIN    | 3   |         | 28  | V    |

| 输出电压       | VBUS   | 3   |         | 22  | V    |

# 7 电气特性

(VIN=24V, VBUS=12V, T<sub>A</sub>=25°C, **除特别说明**。)

| Parameters   | Symbol                   | Test Conditions | MIN | TYP | MAX | UNIT |

|--------------|--------------------------|-----------------|-----|-----|-----|------|

| 供电电源         |                          |                 |     |     |     | •    |

| VIN 输入电源     | $V_{\mathrm{IN}}$        |                 | 3   |     | 28  | V    |

| VIN 输入欠压门限   | V <sub>IN_UVLO</sub>     |                 |     | 3   |     | V    |

| VIN 输入欠压门限迟滞 | V <sub>IN_UVLO_HYS</sub> |                 |     | 400 |     | mV   |

| VDRV 输出电压    | V                        | 待机/开机           |     | 5.5 |     | V    |

| VDRV 捆出电压    | $ m V_{DRV}$             | 关机              |     | 0   |     | V    |

| VDRV 输出电流能力  | T                        | 待机/开机           |     | 40  |     | mA   |

| VDRV 棚田电机能力  | $ m I_{VDRV}$            | 关机              |     | 0   |     | mA   |

| VCC 输出电压     | <b>T</b> 7               | 开机              |     | 5   |     | V    |

| VCC 棚田 电压    | $V_{CC}$                 | 关机/待机           |     | 3.6 |     | V    |

|              |                      | 开机                                  |     | 100 |      | mA |

|--------------|----------------------|-------------------------------------|-----|-----|------|----|

| VCC 输出电流能力   | $I_{VCC}$            |                                     |     | 10  |      | mA |

| <br>输出参数     |                      | ,                                   |     |     |      |    |

| VBUS 电压设置范围  | V <sub>BUS_I2C</sub> | I2C 调压模式<br>dischg_vbus=0x000~0x7ff | 3   |     | 22   | V  |

|              |                      | I2C 调压模式<br>dischg_vbus=0x0C8       |     | 5   |      | V  |

| VBUS 电压      | V                    | I2C 调压模式<br>dischg_vbus=0x258       |     | 9   |      | V  |

| VBO3 电压      | $ m V_{BUS\_I2C}$    | I2C 调压模式<br>dischg_vbus=0x384       |     | 12  |      | V  |

|              |                      | I2C 调压模式<br>dischg_vbus=0x6A4       |     | 20  | •    | V  |

| FB 电压        | $V_{FB}$             | FB 调压模式                             |     | 0.5 |      | V  |

| IBUS 限流设置范围  | $I_{CC\_VBUS}$       | dischg_ibus_limit=0x00~0xff         | 0.5 |     | 6.85 | A  |

|              |                      | dischg_ibus_limit=0x1E              |     | 2   |      | A  |

| IBUS 限流      | т                    | dischg_ibus_limit=0x32              |     | 3   |      | A  |

|              | $I_{CC\_VBUS}$       | dischg_ibus_limit=0x5A              |     | 5   |      | A  |

|              |                      | dischg_ibus_limit=0x78              |     | 6.5 |      | A  |

| IIN 限流设置范围   | I <sub>CC_VIN</sub>  | dischg_iin_limit=0x00~0x77          | 0.1 |     | 12   | A  |

|              |                      | dischg_iin_limit=0x18               |     | 2.5 |      | A  |

| IDI 四次       | T .                  | dischg_iin_limit=0x31               |     | 5   |      | A  |

| IIN 限流       | I <sub>CC_VIN</sub>  | dischg_iin_limit=0x4A               |     | 7.5 |      | A  |

|              |                      | dischg_iin_limit=0x63               |     | 10  |      | A  |

| 工作电流         |                      |                                     |     |     |      |    |

| <b>大扣中</b> 深 |                      | 关闭输出<br>关闭负载接入检测、<br>使能低功耗模式        |     | 40  |      | uA |

| 关机电流         | $ m I_{Q\_STANDBY}$  | 关闭输出<br>打开负载接入检测、<br>使能低功耗模式        |     | 50  |      | uA |

| 待机电流         | ${ m I_{Q_ON}}$      | 关闭输出<br>关闭负载接入检测、<br>禁止低功耗模式        |     | 530 |      | uA |

|              |                      | VBUS=0V<br>关闭负载接入检测、                |     | 540 |      | uA |

|                |                             |                                      |          | 双平内少                              |      |            |

|----------------|-----------------------------|--------------------------------------|----------|-----------------------------------|------|------------|

|                |                             | 禁止低功耗模式                              |          |                                   |      |            |

|                |                             | VIN=24V、VBUS=5V、<br>300KHz、Qg=5.5nC  |          | 1.9                               |      | mA         |

| 输出空载下 VIN 输入电流 | I <sub>DISCHG_NOLOAD</sub>  | VIN=24V、VBUS=12V、<br>300KHz、Qg=5.5nC |          | 2                                 |      | mA         |

|                |                             | VIN=24V、VBUS=20V、<br>300KHz、Qg=5.5nC |          | 2.1                               |      | mA         |

| SWITCHING      |                             |                                      | <u> </u> |                                   |      |            |

|                |                             | freq=0x1                             |          | 200                               |      | kHz        |

| 工及医表           | -                           | freq=0x0                             |          | 300                               |      | kHz        |

| 开关频率           | $F_{SW}$                    | freq=0x2                             |          | 400                               |      | kHz        |

|                |                             | freq=0x3                             |          | 800                               |      | kHz        |

| 异常保护           |                             |                                      |          | N                                 |      |            |

|                | Vvbus_ovp                   | VBUS rising、I2C 调压模式                 |          | V <sub>DISCHG</sub> _<br>VOL*112% |      | V          |

| VBUS 过压保护      |                             | VBUS falling、I2C 调压模式                |          | V <sub>DISCHG</sub> _<br>VOL*106% |      | V          |

|                |                             | VBUS rising、FB 调压模式                  |          | 24                                |      | V          |

|                |                             | VBUS falling、FB 调压模式                 |          | 22.7                              |      | V          |

| VBUS 过载保护      | Vvbus_dischg_o              | VBUS falling、I2C 调压模式                |          | V <sub>DISCHG</sub> _<br>VOL*80%  |      | V          |

|                |                             | VBUS falling、FB 调压模式                 |          | 1.76                              |      | V          |

| VBUS 短路保护      | V <sub>VBUS_DISCHG_SC</sub> | VBUS falling                         |          | 1.76                              |      | V          |

|                |                             | VIN rising                           |          | 30                                |      | V          |

| VIN 过压保护       | VVIN_DISCHG_OVP             | VIN falling                          |          | 28.4                              |      | V          |

| 过热关机门限         | T <sub>DIE_OTP</sub>        | 芯片温度上升                               |          | 150                               |      | $^{\circ}$ |

| 过热关机迟滞         | T <sub>DIE_OTP_HYS</sub>    | 芯片温度下降                               |          | 20                                |      | $^{\circ}$ |

| 自动检测(LSET)     |                             |                                      | •        |                                   |      |            |

| 4.7UH 电感检测门限   | V <sub>LSET_4.7UH</sub>     |                                      | 1.75     |                                   | 2.5  | V          |

| 3.3UH 电感检测门限   | V <sub>LSET_3.3UH</sub>     |                                      | 1.25     |                                   | 1.75 | V          |

| 2.2UH 电感检测门限   | V <sub>LSET_2.2UH</sub>     |                                      | 0.75     |                                   | 1.25 | V          |

| 1UH 电感检测门限     | $V_{LSET\_1UH}$             |                                      | 0.25     |                                   | 0.75 | V          |

| I2C       |                      |     |     |      |     |

|-----------|----------------------|-----|-----|------|-----|

| I2C 速率    | F <sub>I2C_CLK</sub> |     | 100 | 400  | kHz |

| I2C 逻辑低门限 | $V_{\rm IL}$         |     |     | 0.75 | V   |

| I2C 逻辑高门限 | $V_{ m IH}$          | 1.2 |     |      | V   |

### 8 功能描述

SW3203 是一个高效率的同步 4 管双向升降压 DCDC 控制器,支持 3V-28V 输入电压和 3V-22V 输出电压,支持 I2C 和 FB 两种控制方式,支持 2 路负载接入检测和 3 路通路 NMOS 驱动,可以支持多种不同应用场景并简化方案设计。

SW3203 支持关机低功耗模式,使能低功耗模式后,关机状态下漏电流最低为 40uA,可用于静态耗电要求较高的应用。SW3203 还支持输出短路,输出过流,输出过压,过温等保护功能。

### 8.1 BUCKBOOST 引脚定义

在不同的 VBUS 和 VIN 电压下,SW3203 会自动工作在 buck,buckboost,boost 这 3 种模式,三种模式的切换都是无缝进行的,不会在切换的过程中出现 VBUS 或者 VIN 电压突变的情况。另外 SW3203 包含了 PFM/PWM 两种模式,在轻载下,工作于 PFM 模式;在较大负载下,工作于 PWM 模式。同时,SW3203 支持 1uH、2.2uH、3.3uH 和 4.7uH 这 4 种电感感值,支持 200K、300K、400K 和 800K 这 4 种开关频率,可以根据实际方案的性能需要进行灵活调整。

#### 8.1.1 脉冲频率调制 (PFM)

为了提高轻载时的效率,SW3203 在轻载时将会工作在 PFM 模式,当功率下降时,实际的 开关频率会随之降低。当电感平均电流达到 PWM 模式设定值时,SW3203 将会退出 PFM 模式,进入 PWM 模式工作。

另外,虽然工作在 PFM 模式下提高了轻载效率,但是输出纹波也会相应增大,对于输出纹波敏感的应用,可以通过寄存器设置强制 PWM 模式,强制 PWM 模式下 SW3203 轻载工作时也不会进入 PFM。

#### 8.1.2 脉冲宽度调制 (PWM)

当工作在 PWM 模式,在一个周期开始时,当误差放大器输出高于斜波电压,将会开启对应半桥高侧的 NMOS,当误差放大器输出低于斜波电压时,将会开启对应半桥低侧的 NMOS。周期结束时,斜波电压复位,准备开始下一个周期。在切换 MOS 导通的过程中,总是遵循先关后开的原则,以免出现高侧和低侧 NMOS 串通的危险情况。在高侧和低侧 NMOS 都关闭的情况下,电感电流通过高侧或低侧 NMOS 的体二极管续流。

下表为 PWM 工作模式下, Q1-Q4 这 4 个功率 MOS 管的工作状态。

|      | PWM       | 模式        |           |

|------|-----------|-----------|-----------|

| 工作模式 | Buck      | Buckboost | Boost     |

| Q1   | On        | Switching | Switching |

| Q2   | Off       | Switching | Switching |

| Q3   | Switching | Switching | Off       |

| Q4   | Switching | Switching | On        |

### 8.2 输出设置

SW3203 支持外部 FB 调压和内部 I2C 调压,可以兼容不同的协议芯片。同时调压步进和限流设置步进均满足 PPS 的标准。

#### 8.2.1 输出启动

SW3203 默认设置为 FB 模式,上电时输出自动打开,并将 IBUS 输出限流设置为 5.3A,将 IIN 限流设置为 12A。

此外 SW3203 还可以设置默认状态为 I2C 模式,默认设置为 I2C 模式时,SW3203 上电将不会自动打开输出。打开输出需要按照下面的步骤设置:

- (1) 设置输出电压。

- (2) 设置 VBUS/VIN 输出限流值。。

- (3) 打开输出使能。

I2C 模式和 FB 模式可以通过寄存器修改,但上电是否自动打开输出的功能,只与上电时的默认状态相关。

#### 8.2.2 FB 调压

外部 FB 调压模式下, FB pin 的电压固定为 0.5V, 可以根据需要输出的电压选择合适的分压电阻。需要搭配协议 IC 时,建议 R1 选择 100K。

FB 模式下,输出电压计算方式如下:

$$VBUS = 0.5 \times (1 + \frac{R1}{R2})$$

VBUS

R1

FB

GND

输出限流的设置,详见"8.2.3 I2C调压"

#### 8.2.3 I2C 调压

内部 I2C 调压模式下,FB pin 处于 floating 状态,无需再接 FB 电阻。设置好输出电压、输出限流后,打开输出使能就可以打开输出。

VBUS 输出电压可以通过寄存器设置,可设置范围是 3V-22V, 10mV/step。

VBUS 限流可以通过寄存器设置,可设置范围是 0.5A-6.85A, 50mA/step。

VIN 限流可以通过寄存器设置,可设置范围为 0.1A-12A, 100mA/step。

### 8.3 异常保护

SW3203 拥有完善的保护措施: 芯片过温保护、逐周期峰值过流保护、输入欠压保护、输入过压保护、输出过压保护、输出短路保护、输出过流保护等,最大程度的保证设备的安全。

#### 8.3.1 芯片过温保护

SW3203 支持芯片过温保护功能,当 SW3203 温度升高到芯片过温保护阈值并持续 16mS 以上,则认为触发芯片过温异常,关闭输出。芯片过温温度共 4 档可设: 120℃/130℃/140℃/150℃。芯片过温保护触发后,只要芯片温度降低到过温保护阈值-20℃并持续 16mS 以上,芯片退出过温保护,输出重新启动。

#### 8.3.2 VBUS 过压保护

SW3203 支持 VBUS 过压保护功能,当输出电压超过 VBUS 过压保护门限并持续 16mS 以上时,则认为触发 VBUS 过压异常,关闭输出。触发 VBUS 过压异常后,当输出电压低于 VBUS 过压退出门限持续 16mS 以上时,则退出 VBUS 过压异常,恢复输出。

当工作在 FB 调压模式时, VBUS 过压保护门限为 24V, VBUS 过压退出门限为 22.74V。 当工作在 I2C 调压模式时, VBUS 过压保护门限为输出电压设置值的 112%, VBUS 过压 退出门限为输出电压设置值的 106%。

#### 8.3.3 VBUS 过流保护

SW3203 支持 VBUS 过流保护功能,可以在输出端过载的时候关闭输出。当 VBUS 电压低于 VBUS 过流保护门限并持续 32mS,则认为触发 VBUS 过流异常,关闭输出。输出关闭后每隔一定时间会 hiccup 一次,这个 hiccup 时间可由寄存器设为 200mS 或 500mS。

当工作在 FB 调压模式时, VBUS 过流保护门限与短路保护门限一致, 为 1.76V。

当工作在 I2C 调压模式时, VBUS 过流保护门限为输出电压设置值的 80%。

#### 8.3.4 VBUS 短路保护

SW3203 支持 VBUS 短路保护功能,可以在输出端发生短路的时候关闭输出。当 VBUS 电压低于 VBUS 短路保护门限并持续 4mS 以上,则认为触发 VBUS 短路异常,关闭输出。输出关闭后,每隔一定时间会 hiccup 一次。这个 hiccup 时间可由寄存器设为 200mS 或 500mS。

输出 VBUS 短路保护门限为 1.76V。

#### 8.3.5 VIN 欠压保护

SW3203 支持 VIN 欠压保护功能,可以在 VIN 低电时关闭输出。当 VIN 电压低于 VIN 欠压保护门限并持续超过 32mS,则认为触发 VIN 欠压异常,关闭输出。当输入电压高于 VIN 欠压恢复门限,并持续超过 64mS,则退出 VIN 欠压异常,恢复输出

VIN 欠压保护门限为 3V, VIN 欠压恢复门限为 3.4V。

#### 8.3.6 VIN 过压保护

SW3203 支持 VIN 过压保护功能,可以在 VIN 输入过压时禁止输出。当 VIN 电压高于 VIN 过压保护门限并持续超过 100uS,则认为触发 VIN 过压异常,关闭输出。触发 VIN 过压后,当 VIN 电压低于 VIN 过压恢复门限并持续超过 36mS,则认为退出 VIN 过压异常。

VIN 过压保护门限为 30V, VIN 过压恢复门限为 28.4V。

#### 8.3.7 逐周期峰值过流保护

SW3203 支持逐周期峰值过流保护功能,输出过程中,如果电感峰值电流超过12A/14A/16A/18A,将会提前关闭当前模式下的主动管,限制电感峰值电流。

工作在 buck 模式时,使用 VBUS 检流电阻检测电感峰值电流并完成逐周期峰值过流保护。

工作在 boost 模式时,利用 Q2 的 Vds 检测电感峰值电流并完成逐周期峰值过流保护,要求按照 Q2 的实际内阻来设置 Q2 导通内阻的寄存器,保证实际检测到的电感峰值限流与电感峰值电流设置寄存器设置的值更接近。Q2 导通内阻的寄存器可设置值为  $2.5 \text{m}\Omega/7.5 \text{m}\Omega/10 \text{m}\Omega$ 。boost 模式实际的峰值限流值如下。

$$I_{OCP\_ACT} = \frac{R_{DSON\_Q2\_SET}}{R_{DSON\_Q2\_ACT}} \times I_{OCP\_SET}$$

其中  $I_{OCP\_ACT}$  为实际峰值限流值, $R_{DSON\_Q2\_ACT}$  为 Q2 实际的导通内阻, $R_{DSON\_Q2\_SET}$  为寄存器设置的 Q2 导通内阻, $I_{OCP\_SET}$  为寄存器设置的峰值限流值。

#### **8.4 ADC**

SW3203 内置了 12bit 的 ADC,可以采集 VBUS/VIN/IBUS/IIN 等数据。具体计算公式如下。

| 通道          | 描述       | 动态范围         | 计算公式(N为ADC输出码值)       |

|-------------|----------|--------------|-----------------------|

| Vin         | VIN 电压   | 0V-30.72V    | Vin=N*7.5mV           |

| Vbus        | VBUS 电压  | 0V-30.72V    | Vout=N*7.5mV          |

| Iin_dischg  | VIN 端电流  | 0A-20.48A    | Iin_dischg=N*5mA      |

| Ibus_dischg | VBUS 端电流 | 0A-20.48A    | Iout_dischg=N*5mA     |

| Tdie        | 片内温度     | -100°C~200°C | Tdiet=(N-1839)/6.82°C |

#### **8.5 IRO**

SW3203 集成了外部中断引脚 IRQ,开漏结构,使用时推荐通过 10K 电阻上拉。当需要监控的事件发生时,IRQ 将拉低并一直保持低电平直到对应事件的标志位清除。

可监控的事件包括负载检测触发和工作异常等,每一个事件均可以通过寄存器单独设置。

## 8.6 接入检测

SW3203 集成了两路负载接入检测,打开后可以自动识别外部负载接入,简化方案设计。接入检测功能打开后,对应端口上的电压将建立到检测门限以上,负载接入后会拉低此电压到识别门限以下,从而识别到设备接入。

每一次接入检测触发后,如果想继续识别外部负载接入,都需要先关闭该接入检测后再重新打开才能生效。

### 8.7 通路管驱动

SW3203 集成了 3 路 NMOS 通路管驱动,每个通路 MOS 驱动均可独立打开和关闭,无需再增加任何外部电路,简化设计。

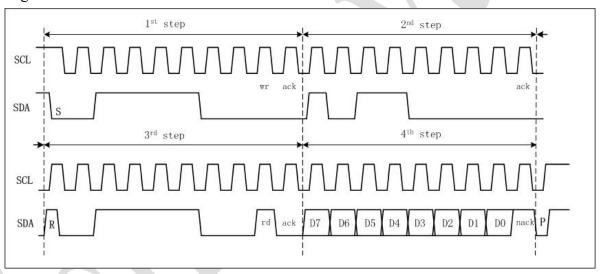

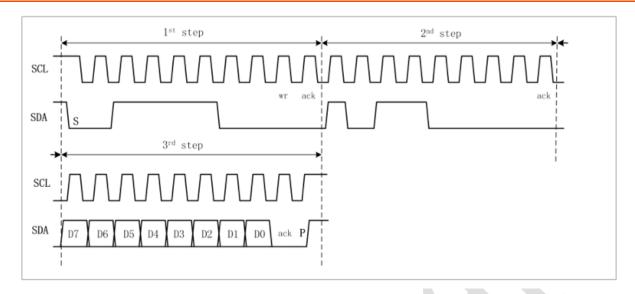

#### 8.8 I2C

SW3203 支持 I2C 接口,支持 100K-400K 通信速率。Master 可通过 I2C 接口读取芯片的状态信息。且 SW3203 共支持 4 个不同的 I2C 地址设置,分别为 0x3C/0x38/0x1C/0x18。 I2C 不支持连续读写。

#### 读操作:

Slave address : 0x3C (读 0x79,写 0x78)

Register address: 0xB0

#### 写操作:

Slave address : 0x3C (读 0x79,写 0x78)

Register address: 0xB0

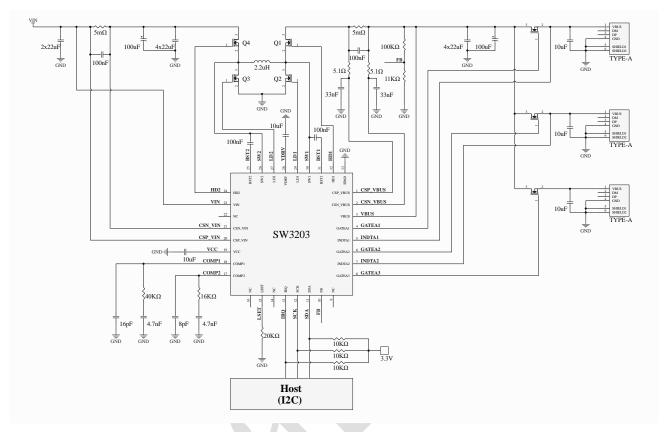

## 9 应用参考

### 9.1 典型应用图

### 9.2 参数配置

#### 9.2.1 电感值选择

LSET 对地接不同的电阻用于配置电感,开关频率选用 800K 时,可选用 1uH 或 2.2uH 电感, VIN 和 VBUS 端的固态电容推荐使用 100uF。开关频率选用 200K/300K/400K 时,推荐选用 3.3uH 或 4.7uH 电感并将 VIN 和 VBUS 端的固态电容增大到 220uF。

LSET 具体电阻设置请参考下表。

| LSET 对地电阻 | 对应电感值  |

|-----------|--------|

| 10K       | 1uH    |

| 20K       | 2.2 uH |

| 30K       | 3.3 uH |

| 43K       | 4.7 uH |

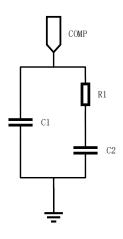

#### 9.2.2 COMP 补偿 RC 参数选择

COMP1 和 COMP2 引脚根据不同电感选择不同的电阻电容参数,其中 COMP1 为 CV 环路

补偿引脚, COMP2 为 CC 环路补偿引脚。 COMP 补偿电路:

#### COMP1 具体设置:

| 电感值    | R1  | C1   | C2    |  |  |

|--------|-----|------|-------|--|--|

| 1uH    | 60K | 16pF | 4.7nF |  |  |

| 2.2 uH | 40K | 16pF | 4.7nF |  |  |

| 3.3 uH | 30K | 16pF | 4.7nF |  |  |

| 4.7 uH | 20K | 16pF | 4.7nF |  |  |

#### COMP2 具体设置:

| 7 111 7 7 2 2 2 2 |     |     |       |

|-------------------|-----|-----|-------|

| 电感值               | R1  | C1  | C2    |

| 1uH               | 8K  | 8pF | 4.7nF |

| 2.2 uH            | 16K | 8pF | 4.7nF |

| 3.3 uH            | 24K | 8pF | 4.7nF |

| 4.7 uH            | 32K | 8pF | 4.7nF |

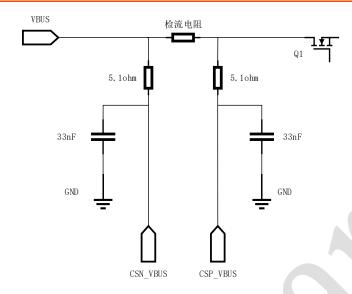

#### 9.2.3 VBUS 检流低通滤波器参数选择

SW3203 基于平均电流模式设计,通过 VBUS 检流电阻监控电感电流,而 PCB 上存在寄生电感导致 CSN\_VBUS-CSP\_VBUS 上产生高频噪声,从而影响检流。当低通滤波器的时间常数在 47nS 到 200nS 之间时,可以很好的滤除高频噪声,并且不会对检流信号产生太大的延迟,保证工作稳定。推荐在 CSN VBUS 与 CSP VBUS 上加入下图所示的滤波电路。

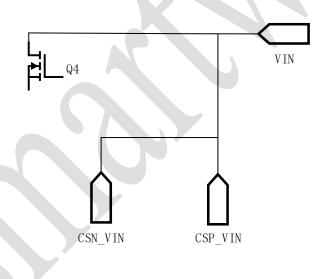

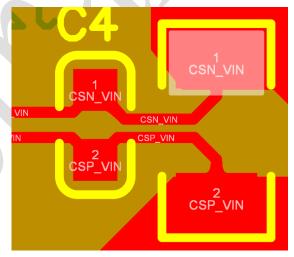

### 9.2.4 VIN 检流

在应用中,如果用不到 VIN 端限流保护,可以去掉 VIN 端的检流电阻,并将 CSP\_VIN 和 CSN\_VIN 短接到 VIN。具体电路连接如下图所示。

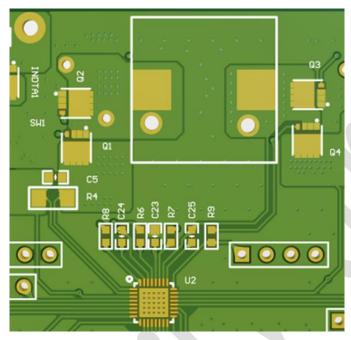

### 10 PCB 布局参考

1. 功率 MOS 管和电感为主要发热器件,适当远离,加强散热;建议 Q1~Q4 功率 MOS 管摆放在芯片的同一侧。

2. 电流采样的引线须采用开尔文接法,从电阻焊盘向里拉出,单独引线 CSP\_VIN、CSN\_VIN 引脚,中间不要引线到其他地方,同样 VBUS 端采样电阻通过电阻直接引线到 CSP\_VBUS、CSN\_VBUS 引脚,线宽为 8mil 或 10mil 即可;与采样电阻并联的 0.1uF 电容靠近采样电阻摆放。

- 3. 一般信号走线(不走大电流)建议线宽 0.2mm(8mil)或 0.25mm(10mil), 芯片 HD1、LD1、SW1、HD2、LD2、SW2 引脚到功率元件至少保持 0.25mm(10mil)以上的宽度。

- 4. 由于电感处信号翻转频率较高,容易影响其他信号线,所以电感底部尽量不走线。

- 5. VCC/VDRV 电容、COMP1、COMP2 的补偿网络靠近 IC 引脚摆放。

- 6. 输入电容尽可能靠近功率 MOS 管电源和接地连接,路径尽可能短;

- 7. FB 的反馈电阻需要靠近 FB 管脚摆放并且需要避开噪声源。

- 8. VBUS、SW1、SW2、VIN、GND 走线尽量宽,最好铺铜,宽度不小于 80mil; SW 的走线要尽可能短,尽量不要换层,大电流网络走线换层时至少 12 个过孔,尽量多打过孔,但要同时考虑底层地的完整性,方便散热。

- 9. 过孔的数量根据换层时过电流大小、散热 PAD 的大小而定。VBUS、SW1、SW2、VIN、GND 换层时推荐打 12 个以上过孔; 其他空余空间建议多打过孔,加强底层与顶层的连接,帮助散热。

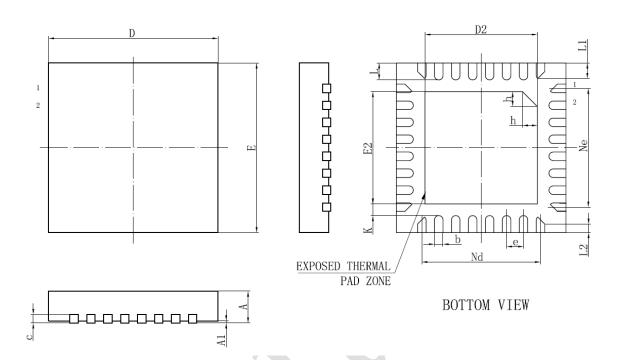

# 11 机械尺寸

## 11.1 封装图

## 11.2 封装尺寸

| Symbol | Dimension in Millimeters |      |      |  |

|--------|--------------------------|------|------|--|

|        | MIN                      | NOM  | MAX  |  |

| A      | 0.70                     | 0.75 | 0.80 |  |

| A1     | 0                        | 0.02 | 0.05 |  |

| b      | 0.15                     | 0.20 | 0.25 |  |

| С      | 0.18                     | 0.20 | 0.23 |  |

| D      | 3.90                     | 4.00 | 4.10 |  |

| D2     | 2.60                     | 2.65 | 2.70 |  |

| e      | 0.40BSC                  |      |      |  |

| Ne     | 2.80BSC                  |      |      |  |

| Nd     | 2.80BSC                  |      |      |  |

| Е      | 3.90                     | 4.00 | 4.10 |  |

| E2     | 2.60                     | 2.65 | 2.70 |  |

| L      | 0.35                     | 0.40 | 0.45 |  |

| L1     | 0.30                     | 0.35 | 0.40 |  |

| L2     | 0.15                     | 0.20 | 0.25 |  |

| h      | 0.30                     | 0.35 | 0.40 |  |

### 12 版本历史

V1.0 初始版本;

#### 责任及版权申明

珠海智融科技股份有限公司(以下简称"智融科技")可能随时对所提供的产品、服务及本文件作出修改或更新,且不另行通知。客户应在下订单前获取最新的相关信息,并确认这些信息是否完整且是最新的。

本文件所含信息仅为您提供便利,智融科技不对这些信息作任何明示或暗示、书面或口头、 法定或其他形式的声明或保证,包括不但限于产品的用途、特性、使用情况、适销性等方面。 智融科技对这些信息及不合理使用这些信息而引起的后果不承担任何责任。

智融科技对应用帮助或客户产品设计不承担任何义务。客户应对其使用智融科技的产品和应用自行负责。客户应提供充分的设计与操作安全验证,且保证在将智融产品集成到任何应用程序中时不会侵犯第三方知识产权,如发生侵权行为智融科技对此概不承担任何责任。

在转售智融科技产品时,如果对该产品参数及其陈述相比存在差异或虚假成分,则会自动丧失智融科技相关产品的所有明示或暗示授权,且对此不正当的、欺诈性商业行为,智融科技保留采取一切合法方式维权。智融科技对任何此类虚假陈述均不承担任何责任或义务。

本文件仅在没有对内容进行任何篡改且带有相关授权、条件、限制和声明的情况下才允许 进行复制,否则智融科技有权追究其法律责任。智融科技对此类篡改过的文件不承担任何责任 或义务。复制如涉及第三方的信息应当服从额外的限制条件。